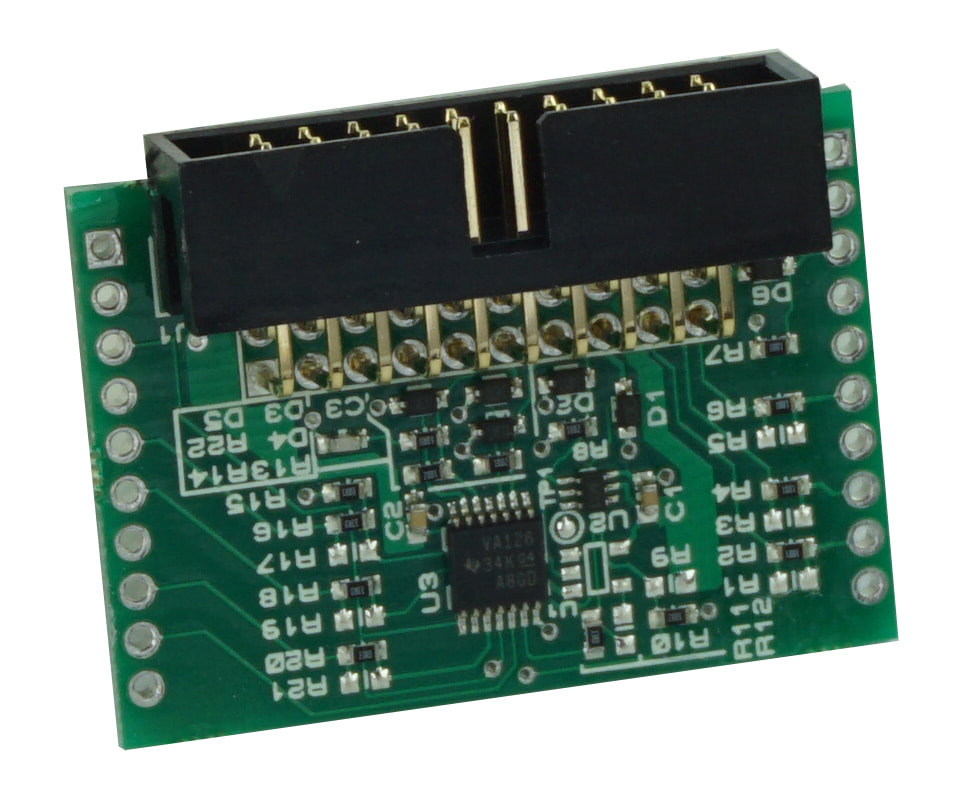

JTAG Bypass Module (only required for native XJTAG SW control)

About

When a J-Testr is used with a JTAG system that has only one physical TAP (e.g. XJTAG XJLink1 ) or a single logical TAP (e.g. XJTAG XJLink2) the JTAG chain is required to be bypassed when the UUT is not powered.

Bypassing the JTAG chain also allows significantly faster communication to the J-Testr when communicating using the Native JTAG interface as it will remove large JTAG chains whilst communicating with the J-Testr.

The Interposer Bypass Card circuit is open source to allow the user to optionally intergrate directly to the interposer with any JTAG system they require.

NOTE:

Bypass is not required for most JTAG systems that have multiple TAPS that can be individually controlled.

Bypass is not required when communicating to the J-Testr with the Ethernet interface

Bypassing the JTAG chain also allows significantly faster communication to the J-Testr when communicating using the Native JTAG interface as it will remove large JTAG chains whilst communicating with the J-Testr.

The Interposer Bypass Card circuit is open source to allow the user to optionally intergrate directly to the interposer with any JTAG system they require.

NOTE:

Bypass is not required for most JTAG systems that have multiple TAPS that can be individually controlled.

Bypass is not required when communicating to the J-Testr with the Ethernet interface

Schematic

|

| ||

Bill of Materials

| Interposer Bypass Card BOM |