J-Testr Core Communications Architecture

As a modern functional test system, the J-Testr Core supports both Ethernet and JTAG interfaces for ultimate communications flexibility

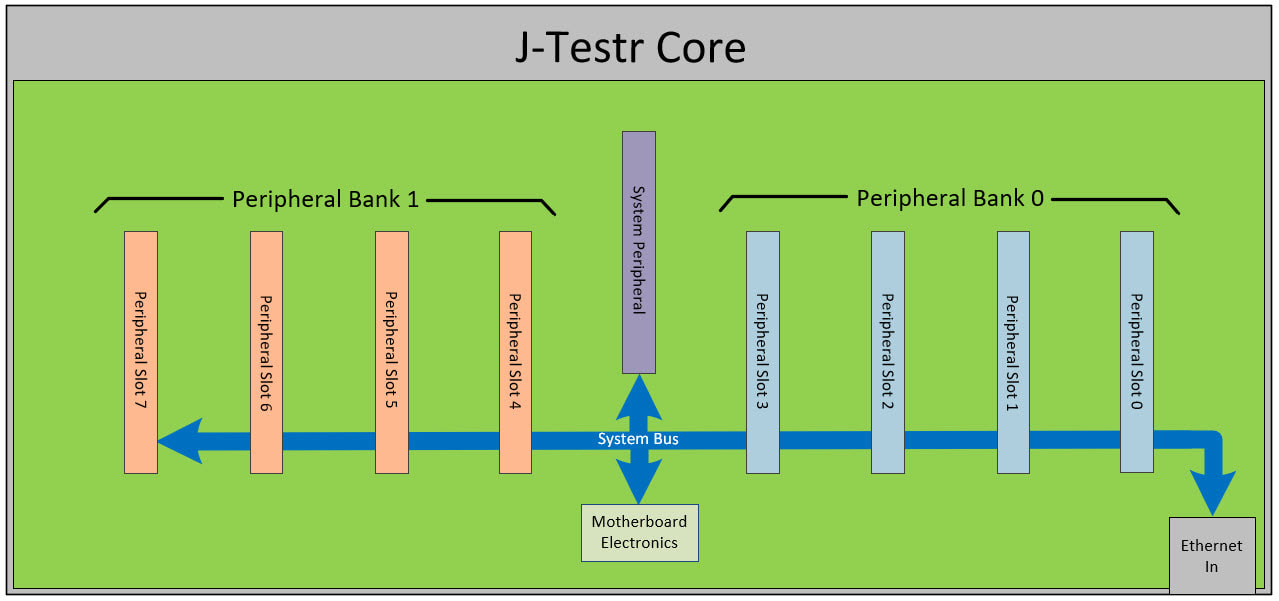

Ethernet Communications

Ethernet communications provides electrical isolation from electrically noisy PC systems but also allows the J-Testr Core to be part of any network and as such is capable to be connected and controlled remotely if required. This allows companies that have production if far locations to connect and assist in any production issues without travelling to the location.

The Ethernet communications provides communication access to all peripheral cards and the motherboard situated in the J-Testr Core.

Ethernet communications provides electrical isolation from electrically noisy PC systems but also allows the J-Testr Core to be part of any network and as such is capable to be connected and controlled remotely if required. This allows companies that have production if far locations to connect and assist in any production issues without travelling to the location.

The Ethernet communications provides communication access to all peripheral cards and the motherboard situated in the J-Testr Core.

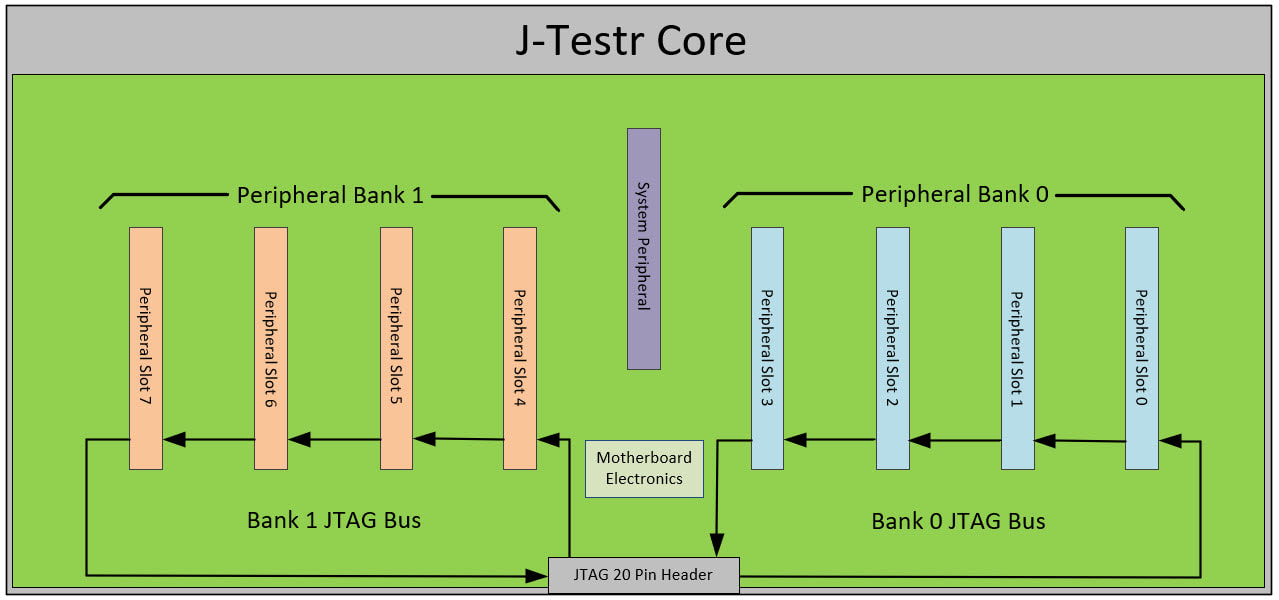

JTAG Boundary Scan Communication

Boundary Scan is becoming common place when functionally testing UUTs as it allows access to the internal pins of devices situation on modern UUTs. The J-Testr Core allow I/O resources, within certain peripheral cards, to be controlled directly from a JTAG interface (as well as direct control from the ethernet interface) such that Boundary Scan software suites can make full close loop testing of UUT IOs without any extra coding.

Boundary Scan is becoming common place when functionally testing UUTs as it allows access to the internal pins of devices situation on modern UUTs. The J-Testr Core allow I/O resources, within certain peripheral cards, to be controlled directly from a JTAG interface (as well as direct control from the ethernet interface) such that Boundary Scan software suites can make full close loop testing of UUT IOs without any extra coding.

Within the J-Testr Core each peripheral bank, of 4 slots, has an individual JTAG chain connection. Peripheral cards not fitted or with no JTAG functions are automatically bypassed to keep the JTAG chain intact.