|

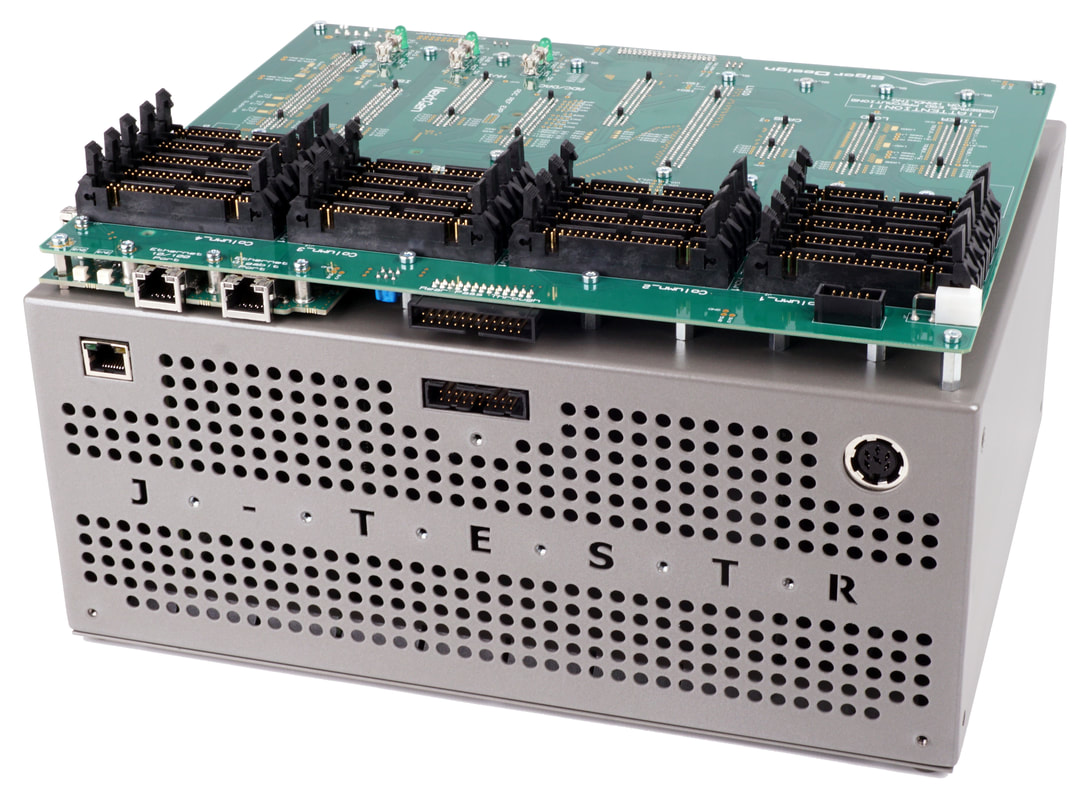

.J-Testr Core is at the very heart of all J-Testr functional test systems. The J-Testr Core provides a highly compact test engine that contains modular stimulation / measurement peripheral cards and the power architecture and communication architecture required to implement advanced and flexible functional test solutions.

|

J-Testr Core is specifically designed to be highly compact to aid easy integration into test fixtures allowing significant reduction in cabling, reducing cable losses and signal integrity issues related to long cabling.

However, despite its small size, the J-Testr Core can also be used as a stand-alone test system due to its top mounted Interposer PCB that is easily customized to route the J-Testr Core stimulation/measurements signals to the required connections for a UUT. This makes the J-Testr Core test platform highly versatile and highly reusable.

The available modular peripheral cards for the J-Testr Core include both ‘power supply’ and ‘electronic load’ functions eliminating the requirement for separated bulky power supplies and electronic loads. This further simplifies integration/deployment and reduces the amount of cabling required, in some test setups all cables can be eliminated altogether!

However, despite its small size, the J-Testr Core can also be used as a stand-alone test system due to its top mounted Interposer PCB that is easily customized to route the J-Testr Core stimulation/measurements signals to the required connections for a UUT. This makes the J-Testr Core test platform highly versatile and highly reusable.

The available modular peripheral cards for the J-Testr Core include both ‘power supply’ and ‘electronic load’ functions eliminating the requirement for separated bulky power supplies and electronic loads. This further simplifies integration/deployment and reduces the amount of cabling required, in some test setups all cables can be eliminated altogether!

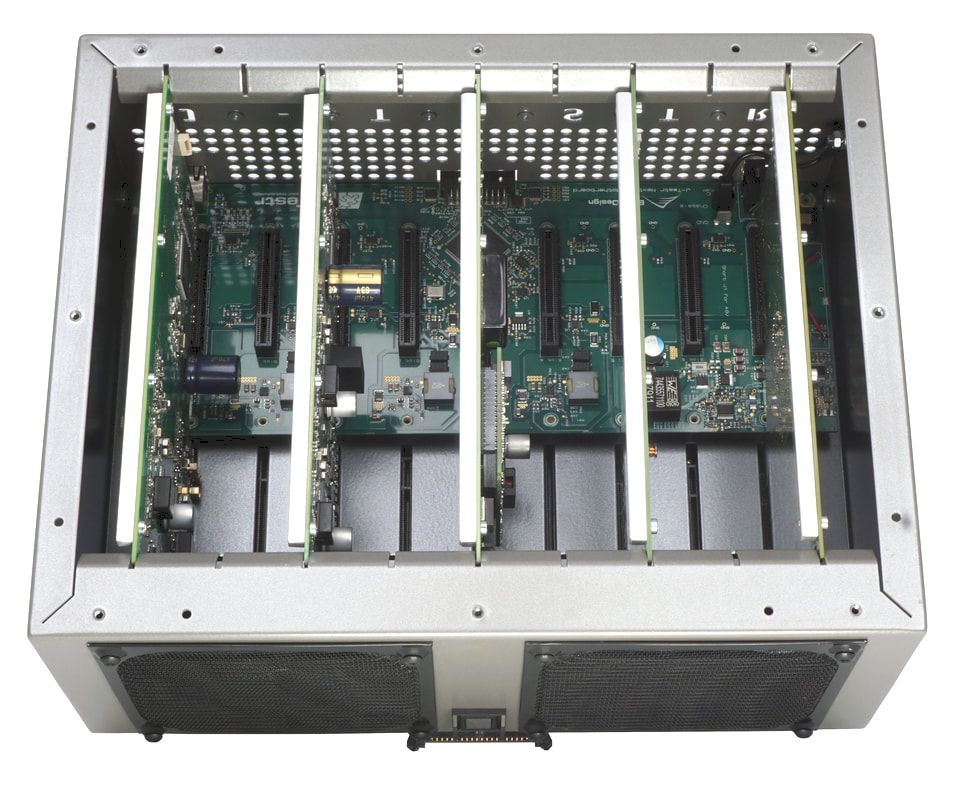

J-Testr Core can be configured with any combination of stimulation/measurement peripheral cards as required by the test application. There are locations for up to 8 peripheral cards to be situated inside the core, each peripheral card has specific stimulation/measurement functions such that the right configuration can be built for the target UUTs to be tested.

The interposer that sits on top of the J-Testr Core allows transition between the peripheral card’s stimulation/measurement signals and the UUT connection required. This card can be customized* by the customer or but Eiger Design or one of our integration partners. Eiger Design also have complete ‘off the shelf’ systems available using a pre-designed Generic test Interposer (GTI).

*Note customizations can include addition user specific test electronics or even expand tester functions with multiplexers, relay, buffers, etc.

The interposer that sits on top of the J-Testr Core allows transition between the peripheral card’s stimulation/measurement signals and the UUT connection required. This card can be customized* by the customer or but Eiger Design or one of our integration partners. Eiger Design also have complete ‘off the shelf’ systems available using a pre-designed Generic test Interposer (GTI).

*Note customizations can include addition user specific test electronics or even expand tester functions with multiplexers, relay, buffers, etc.

|

Unique Peripheral Cards

Our unique peripheral cards are shaped to allow the direct plugging from the J-Testr Core to the Interposer in one action and require no cabling. This concept allows much improved signal losses and signal integrity issues related to cabling and interconnects present in more tradition test systems Available functions include: Power Supplies, Electronic Loads, Precision ADC/DAC Channels, High Seed Timer IO, Low Voltage IO (JTAG compatible), High Voltage IO (JTAG compatible), CAN/RS422/RS485, User IO (I2C, UART, SPI, PWM, Timer features), +others Learn more about the available peripheral cards here |

|

Internal Motherboard and System Peripheral

All J-Testr Core platforms have internal fixed system electronics that include an internal motherboard and system peripheral card that take care of all the required system functions and provide the power architecture and communication architecture to the rest of the test system. The system electronics take care of cooling, power management, power measurement , power switching , communications interfaces, System IO resources, J-Safe Measure features, other J-Safe functions. |

|

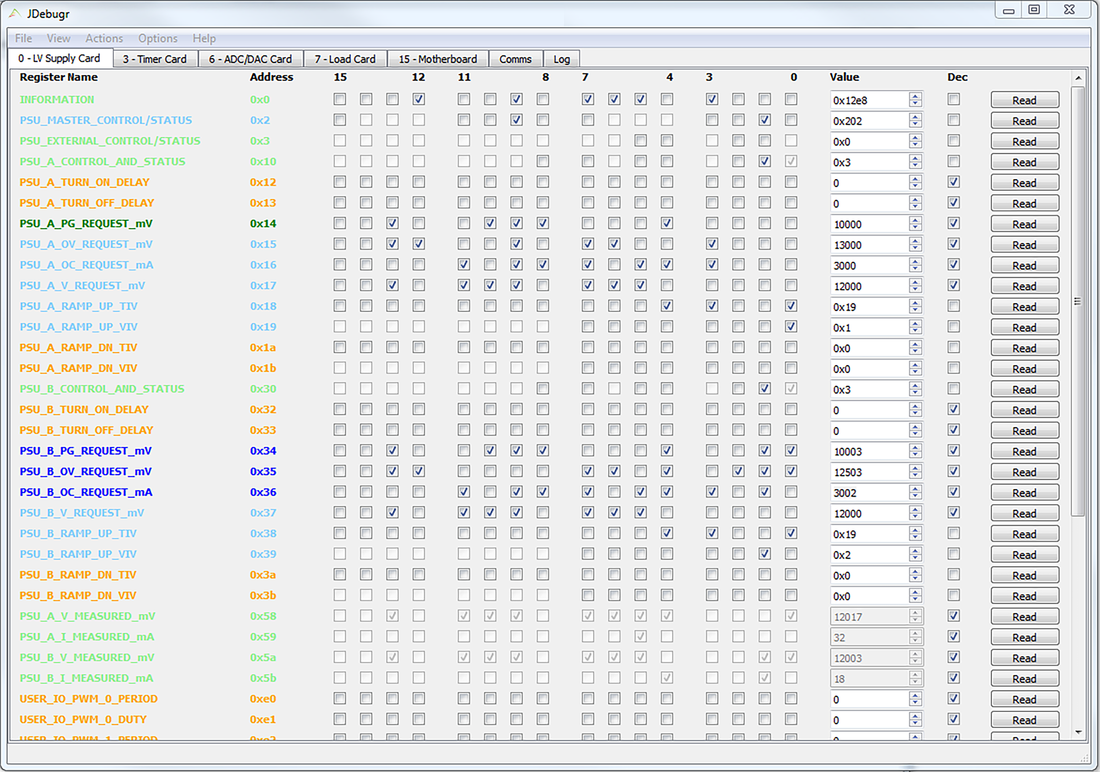

Software

At the lowest level the J-Testr Core is controlled via a simple memory mapped 16-bit register sets, accessed via the ethernet port, that behaves extremely similar to a micro-controller device. This interface was designed to make any engineer with some micro-controller knowledge instantly at home. This interface makes the J-Testr core be able to be used by any software platform with access to a socket interface. However Eiger design supports higher level drivers (function wrappers) in native ATEASY and generic DLL packages. The later DLL can be used with common plateforms like TestStand, LabVIEW, C#, C++, python and many more. |

|

Simple and familiar Debugging

All software needs simple and effective debugging tools to speed the development process. The J-Testr Cores memory mapped 16-bit register sets are supported by the open source J-Debugr software tool which allow a 'real-time' view of all registers within the core and its peripherals. Designed purposely to look very similar to micro-controller debugging tools and with features like time-stamped logging and color-coded actions user with any basic knowledge of micro-controllers are placed in an instantly familiar environment. Click here for more information. |

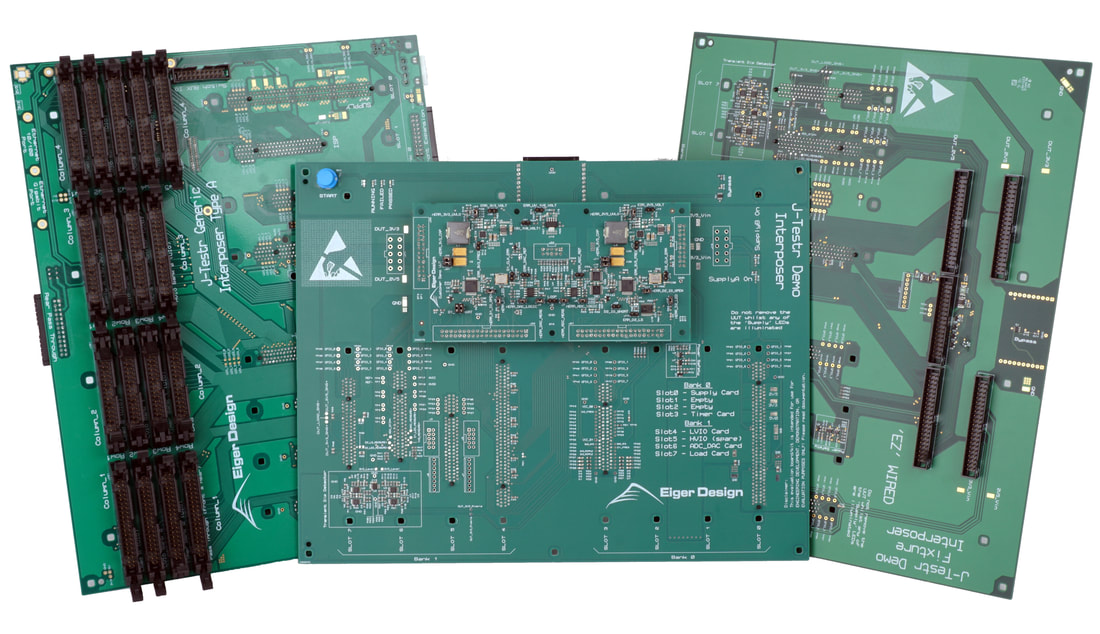

Customizable or Generic Interposer

The Interposer PCB, that is located on the top of the J-Testr, is responsible to route the stimulation / measurement signals from the internal peripheral cards to the UUT. The same PCB can be used to add extra tester functions if required by the test application.

Interposer PCB are easily customizable, using standard PCB design processes, by the customer or by the Eiger Design to the customers requirements. Generic test interposers (GTI) are also available and are used as part of our 'Off the Self' NextGen complete test solutions.

The Interposer PCB, that is located on the top of the J-Testr, is responsible to route the stimulation / measurement signals from the internal peripheral cards to the UUT. The same PCB can be used to add extra tester functions if required by the test application.

Interposer PCB are easily customizable, using standard PCB design processes, by the customer or by the Eiger Design to the customers requirements. Generic test interposers (GTI) are also available and are used as part of our 'Off the Self' NextGen complete test solutions.