J-Testr Core User I/Os

|

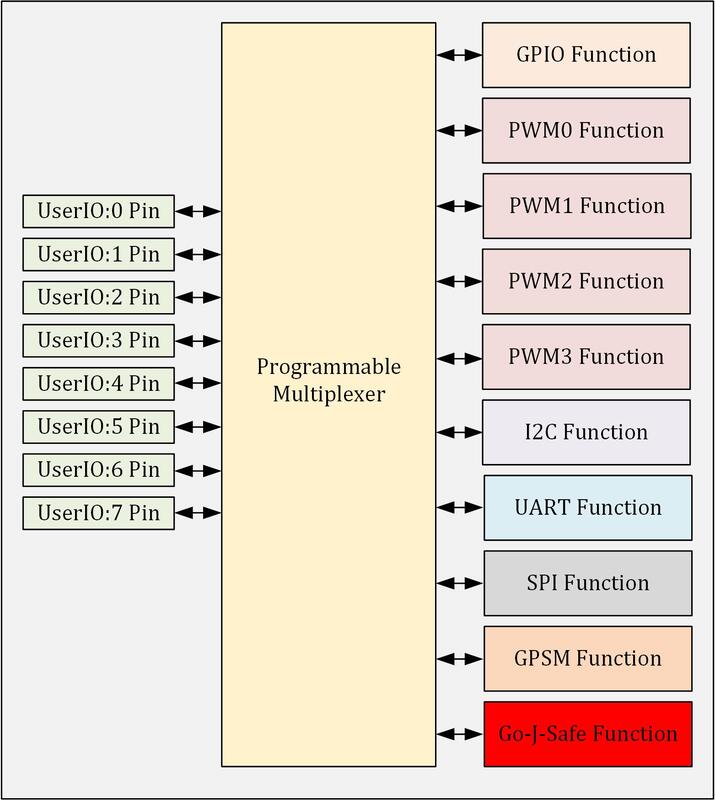

Each simulation and measurement peripheral card in a J-Test Core provides 8 general purpose User IOs which can be used to control and/or read custom circuitry or UUT functions. The User IOs provide special hardware functions that can be multiplexed to any of the User IO pins.

These hardware functions provided by the user IO are described below: Default (No special function selected)

The User IO lines can be configured and used as either input, push/pull or open collector. UART (Universal Asynchronous Receiver-Transmitter)

The User IO lines can be selected to be either a transmit (TX) or receive (RX) to a programmable hardware UART function with internal buffers |

SPI (Serial Peripheral Interface)

The User IO lines can be selected to be either Master Out/Slave In (MOSI), Master In/Slave Out (MISO), Serial Clock (SCLK) or Chip Select (CS) to a programmable hardware SPI function.

The User IO lines can be selected to be either Master Out/Slave In (MOSI), Master In/Slave Out (MISO), Serial Clock (SCLK) or Chip Select (CS) to a programmable hardware SPI function.

PWM (Pulse Width Modulation)

The User IO lines can be selected to be a modulating PWM signal to one of four programmable PWM engines.

The User IO lines can be selected to be a modulating PWM signal to one of four programmable PWM engines.

GPSM (General Purpose Signal Monitor)

The User IO lines can be selected to be a GPSM input to General-Purpose Signal Monitor function able to monitor a signal, or a set of 2 signals, to measure common timing information. Such information includes frequency, pulse width, duty, propagation delays, etc.

The User IO lines can be selected to be a GPSM input to General-Purpose Signal Monitor function able to monitor a signal, or a set of 2 signals, to measure common timing information. Such information includes frequency, pulse width, duty, propagation delays, etc.

I2C (Inter-IC)

The User IO lines can be selected to be either Serial Data (SDA) or Serial Clock (SCK) to a programmable hardware I2C function which can have an I2C master or a slave function

The User IO lines can be selected to be either Serial Data (SDA) or Serial Clock (SCK) to a programmable hardware I2C function which can have an I2C master or a slave function

Go J-Safe

The User IO lines can be selected to become a ‘Go J-Safe’ inputs which will place the system in an immediate J-Safe protection state when transitioned from a high to low logic level.

The User IO lines can be selected to become a ‘Go J-Safe’ inputs which will place the system in an immediate J-Safe protection state when transitioned from a high to low logic level.