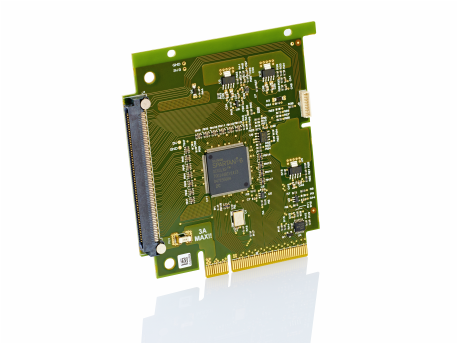

Development Peripherial Card

Features• Enables custom test HW with signal speeds <=3GHz

• 2 Dedicated FPGA banks available for custom usage • 24 High-speed IO lines per bank • Programmable VccIO levels per bank • All customer IO lines impedance controlled • 2V5, 3V3, 5V and HV supplies available for custom HW • Sample VHDL code available • All mechanical data available to the customer • 50 MHz frequency oscillator • On-board EEPROM |

| ||

About

The development peripheral card is a truly unique concept that allows the user to develop their own J-Testr peripheral cards.

The development card provides the customer designed side with 48 high-speed capable IO lines, and four different supply voltages ranging from 2.5V to the system input voltage (HV). The IO lines are provided from two dedicated FPGA IO banks for which the user can program the required VccIO voltage for the application. All provided IO lines are impedance controlled with series terminators to allow high-speed operation.

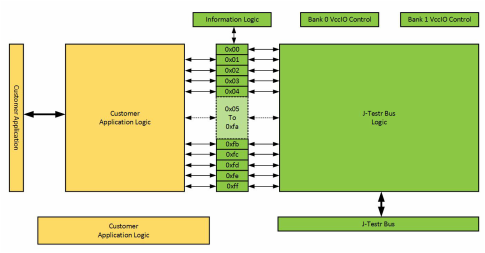

All electronics for interfacing to the J-Testr system is included on the development card, so the user only has to consider their own application. The provided FPGA code implements all the J-Testr bus logic to the register interface leaving the user free to implement their logic.

All electronics for interfacing to the J-Testr system is included on the development card, so the user only has to consider their own application. The provided FPGA code implements all the J-Testr bus logic to the register interface leaving the user free to implement their logic.

The FPGA code also provides the necessary control logic for the VccIO voltages and the ‘Information logic’ used to provide information about the card to the J-Testr system.

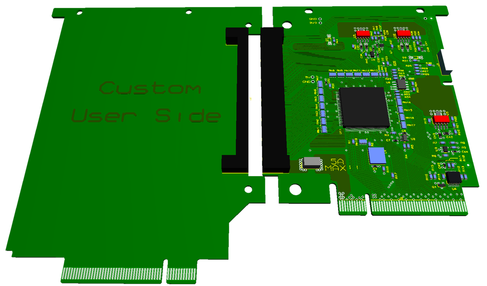

All mechanical data required for the user custom side is provided in both Gerber and DXF format. The customer is free to decide the inter-connection to the interposer, however the standard PCIe connectors, used throughout the J-Testr, provide cost effective high performance capability up to 3GHz.

The J-Testr development concept opens up endless opportunities for users to integrate their own test hardware into the J-Testr system making full use of the available system resources.

Please contact Eiger Design GmbH support at [email protected] for further information.

All mechanical data required for the user custom side is provided in both Gerber and DXF format. The customer is free to decide the inter-connection to the interposer, however the standard PCIe connectors, used throughout the J-Testr, provide cost effective high performance capability up to 3GHz.

The J-Testr development concept opens up endless opportunities for users to integrate their own test hardware into the J-Testr system making full use of the available system resources.

Please contact Eiger Design GmbH support at [email protected] for further information.