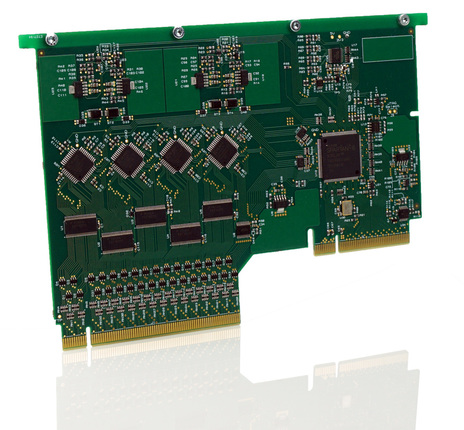

LV IO Peripheral Card

Features• 128 general purpose IOs

• Banked into 4 sets of 32 IOs • JTAG or Ethernet controlled • Programmable VccIO voltage per bank (1.4V to 3.4V) • Integrated accurate measurement of VccIO voltage • 5V tolerant inputs • Over-voltage input protection • Works with any JTAG sofware (BSDL file supplied) • Very simple operation • Global I/O Enable/Disable • Pin to Pin compatible with JTAG IO peripheral card • 8 User I/Os with UART, SPI, I2C, PWM, GoJ-Safe & GPSM features* |

| ||

About

The LV IO peripheral card gives the user 128 general purpose IOs which can be controlled from either the Ethernet communications, via the system bus, or from a boundary scan bus/chain. This allows the user ultimate flexibility to use the card within an Ethernet controlled system, or to make full utilization of the powerful IO testing features provided by JTAG boundary scan testing tools.

The IOs are split into four banks of 32 IOs, each of which have independently programmable VccIO voltages ranging from 1.4V to 3.4V. Input voltages up to 5V can be tolerated due to the on- board input level shifters

Fully protected and adjustable power supplies, per bank, are integrated to save the user from providing the VccIO voltages externally.

These adjustable supplies enable the user to dynamically control the VccIO voltages during testing. This allows IO lines to be tested at different voltage levels, hence achieving better test coverage.

An accurate high resolution 16 bit voltage measurement system is also included to allow verification (self-test) of the VccIO voltages.

With 'test in mind' all IO lines are protected against over-voltage as it is never known what voltages untested UUTs could present to these IO lines. A Global IO enable line allows the user to 'float' the IO lines until the UUT is fully powered.

Since IO cards are low power peripherals, the number of IO cards per J-Testr system is only limited by the number of peripheral card slots. This allows up to 8 per system, equating to 1,024 I/Os, enabling the system to be used for cable testers especially when combined with the powerful IO testing features of some JTAG Tools.

Finally, as with all bus connected peripherals, the ADC/DAC peripheral provides 8 general purpose User IOs which can be used to control and/or read custom circuitry on the interposer. The IOs can provide special hardware functions such as 16-bit PWM, UART, SPI, I2C and GPSM (General Purpose Signal Monitor for measuring freq/duty/pulse-width etc.) that can be multiplexed to any of the IO pins.

*The user GPIOs share the output connector pins with standard IOs, the user can dynamically select if the standard IO or the user GPIOs route to the connector.

The IOs are split into four banks of 32 IOs, each of which have independently programmable VccIO voltages ranging from 1.4V to 3.4V. Input voltages up to 5V can be tolerated due to the on- board input level shifters

Fully protected and adjustable power supplies, per bank, are integrated to save the user from providing the VccIO voltages externally.

These adjustable supplies enable the user to dynamically control the VccIO voltages during testing. This allows IO lines to be tested at different voltage levels, hence achieving better test coverage.

An accurate high resolution 16 bit voltage measurement system is also included to allow verification (self-test) of the VccIO voltages.

With 'test in mind' all IO lines are protected against over-voltage as it is never known what voltages untested UUTs could present to these IO lines. A Global IO enable line allows the user to 'float' the IO lines until the UUT is fully powered.

Since IO cards are low power peripherals, the number of IO cards per J-Testr system is only limited by the number of peripheral card slots. This allows up to 8 per system, equating to 1,024 I/Os, enabling the system to be used for cable testers especially when combined with the powerful IO testing features of some JTAG Tools.

Finally, as with all bus connected peripherals, the ADC/DAC peripheral provides 8 general purpose User IOs which can be used to control and/or read custom circuitry on the interposer. The IOs can provide special hardware functions such as 16-bit PWM, UART, SPI, I2C and GPSM (General Purpose Signal Monitor for measuring freq/duty/pulse-width etc.) that can be multiplexed to any of the IO pins.

*The user GPIOs share the output connector pins with standard IOs, the user can dynamically select if the standard IO or the user GPIOs route to the connector.